Este tutorial discutirá como implementar registros de mudança no Verilog. Podemos sintetizar o registro descrito e baixá-lo em um FPGA para testar em hardware real. Os registros de mudança Verilog são componentes essenciais em projetos de hardware digital, e entender como implementá-los é fundamental para o desenvolvimento de circuitos eficientes e funcionais.

Características e conceitos básicos do Verilog Shift Register

Na sua forma mais simples, um registro de turno consiste em conectar vários elementos de armazenamento, como flip-flops, em série, onde a saída de um elemento de armazenamento entra na entrada do próximo. Um sinal de clock comum controla os elementos de armazenamento.

Digamos que estamos usando flip-flops com ponta positiva. Considere os flip-flops com os rótulos 0 e 1 conforme a imagem acima (ff0 e ff1). A entrada para ff0 é a entrada para o registro de deslocamento. A entrada para ff1 é a saída de ff0, que também é o valor atual de ff0. Em uma borda do clock positivo, ff0 capturará sua entrada e ff1 capturará o valor atual de ff0. Se todos os flip-flops começarem a redefinir para 0 e mantivermos a entrada do registrador de turno em 1, uma borda de clock positiva fará com que ff0 capture 1. No segundo limite positivo do clock, o ff1 captura 1 porque ele amostrou a saída de ff0 conforme a figura abaixo.

Em cada borda do clock positivo sucessivo, o 1 “mudará” para o próximo flip-flop da cadeia até que apareça na saída do registro de deslocamento, que é a saída de ff3 no registro de deslocamento de 4 bits mostrado acima. Se mantivermos a entrada em 1 durante esse período, o registro agora conterá todos os 1s.

Código Verilog Shift Register

Verilog é uma linguagem de descrição de hardware, ou HDL, que descreve o hardware real do circuito lógico. Por esse motivo, existem vários aspectos do Verilog que são diferentes das linguagens de programação de software típicos. Há duas coisas importantes a serem lembradas ao escrever o código Verilog:

• Assim como em um circuito real, algumas partes do código Verilog são executadas simultaneamente, não sequencialmente ou linha por linha, como em um programa de software de thread único.

• Nem todas as construções da Verilog podem ser sintetizadas ou transformadas em um circuito lógico real.

Nosso objetivo é escrever código sintetizável neste exemplo. Isso também nos permitirá baixar nosso código em um FPGA para realmente vê-lo em ação.

Declaração do módulo

Começaremos com uma declaração de módulo:

module shiftReg4(

input shift_in,

input clock,

output shift_out

);Os módulos formam os componentes básicos de um projeto baseado em Verilog. Com o nosso registro de turnos declarado em um módulo, podemos instanciar quantas cópias desejar, conectando como gostamos em um circuito maior. As instruções de entrada e saída são declarações de porta, elas determinam quais conexões estarão disponíveis quando instanciamos nosso registro de turnos. Por enquanto, temos apenas uma entrada de turno, uma entrada de clock e uma saída de turno.

Reg

Em seguida, precisamos definir o circuito e as conexões com fio para o nosso registro de turno. Como no diagrama acima, usaremos quatro flip-flops para esse registrador de deslocamento de 4 bits. Podemos criar um flip-flop usando a palavra-chave reg:

reg bit0;

reg bit1;

reg bit2;

reg bit3;

assign shift_out = bit3;Aqui temos quatro flip-flops chamados de bit0 à bit3. O flip-flop bit0 terá sua entrada conectada à porta shift_in, onde cuidaremos disso no próximo bloco de código. O flip-flop bit3 terá sua saída conectada à porta shift_out, e conseguimos isso com uma instrução de atribuição, que pode ser usada para cabeamento e lógica combinatória.

Bloqueio processual

Agora, precisamos dizer à Verilog o que fazer com esses flip-flops, e realizamos isso em um bloco processual. Usamos um bloco processual para definir lógica combinacional ou sequencial, mas, neste exemplo, usaremos apenas para lógica sequencial.

always @(posedge clock) begin

bit3 <= bit2;

bit2 <= bit1;

bit1 <= bit0;

bit0 <= shift_in;

end

endmoduleO bloco processual começa com a palavra-chave always, seguida por uma lista de sensibilidade. A lista de sensibilidade informa à Verilog quando avaliar as instruções no bloco, nesse caso, avaliamos o bloco em cada extremidade do clock positivo (@posedge clock). Quando o bloco é acionado em uma borda do clock positiva, simplesmente mudamos o conteúdo de cada flip-flop para o próximo flip-flop da cadeia. Portanto, o bit3 obtém o que estava anteriormente no bit2, o bit2 obtém o que estava no bit1 e assim por diante. Observe que delineamos onde o bloco começa e termina com instruções de início e fim.

Módulo final

Finalmente, finalizamos nosso módulo com uma instrução endmodule. Parabéns, você acabou de criar um registro de turno Verilog de 4 bits.

Considerações práticas: indexação e operador de turno

Criamos nosso código Verilog para combinar exatamente com o circuito que imaginávamos, com quatro flip-flops separados conectados em série. Isso é ótimo para saber exatamente o que será sintetizado, mas torna-se tedioso se tivermos que declarar manualmente todos os flip-flops em nosso design. Felizmente, o Verilog possui muitos atalhos diferentes, e aqui podemos usar a indexação e o operador shift:

reg [3:0] bits;

assign shift_out = bits[3];

always @(posedge clock) begin

bits <= bits << 1;

bits[0] <= shift_in;

endIsso é muito mais compacto! Por exemplo, declaramos um registro de 4 bits de uma só vez com a notação de colchete “[3: 0]”, o que indica que o bit 3 é o bit mais significativo (MSB). No entanto, note que temos que mudar nossa declaração de atribuição para conectar o bit 3 do registrador ao nosso sinal shift_out. Dessa forma, agora, em vez de escrever instruções de bloco procedurais para alterar individualmente cada bit, podemos usar uma única instrução com o operador shift left (<<) para realizar o que queremos. Assim, em cada clock positivo, o registro de 4 bits desloca os dados uma posição para a esquerda e aciona o novo MSB em shift_out.

Observe também que essa implementação facilita a alteração da ordem dos turnos. Atualmente, estamos mudando de LSB para MSB, mas podemos mudar isso facilmente de MSB para LSB. Tente isso por conta própria para praticar.

Síntese em Verilog

Vale lembrar que no Verilog, apenas declarar um nó como reg não cria automaticamente um flip-flop. É aí que entra o princípio da síntese e do código sintetizável. O nó de registro mantém seu valor até que atribuamos outro valor. Quando sintetizamos o código para criar estruturas de hardware reais, isso pode resultar em um flip-flop, o que geralmente é desejado, uma trava, o que geralmente não é desejado, ou um erro, dependendo de como atribuímos o nó.

Colocar “@posedge clock” em nossa lista de sensibilidade e além disso, ter o cuidado de atribuir sempre a todos os sinais reg no bloco processual garantem que obteremos os flip-flops que esperamos.

Usos e aplicações

Usamos registros de turnos em situações nas quais precisamos converter dados paralelos, normalmente utilizados internamente em um microprocessador ou outro ASIC, em dados seriais, geralmente utilizados para comunicação entre componentes em um PCB ou entre dois PCBs separados.

Para essa finalidade, normalmente adicionamos um sinal de carga e fios a cada uma das entradas individuais de flip-flop no registro de deslocamento, para que possamos carregar dados paralelos no registro de deslocamento de uma só vez e depois deslocá-los pouco a pouco.

Para implementar protocolos de comunicação serial como I2C e SPI, usamos uma máquina de estado para controlar quando retiramos os bits de dados individuais do registro para atender aos requisitos do esquema que escolhemos. Também adicionamos fios às saídas de cada flip-flop individual para que um dispositivo possa receber dados seriais pouco a pouco e depois lê-los fora do registro de turnos em paralelo quando trocamos todos os bits.

Conclusão

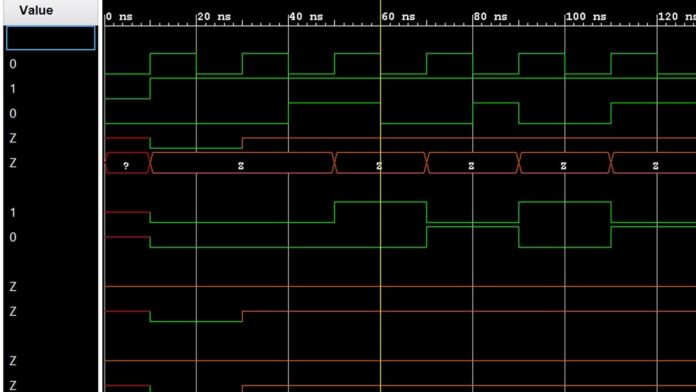

Neste tutorial, discutimos como implementar um registro de turno básico no Verilog. Em seguida, um fluxo de trabalho típico envolveria a criação de um banco de testes para instanciar nosso novo registro de turno e direcionar algumas entradas, assim, podemos verificar a operação correta na simulação antes de sintetizar o código e fazer o download para um FPGA para teste em hardware real.

Caso tenha alguma dúvida ou sugestão quanto a este tutorial, por favor, não hesite em deixar um comentário abaixo. Ademais, espero que tenha gostado deste pequeno exemplo.